Fußgänger im Blick

Embedded-Systeme sind wegen ihrer Größe und Effizienz für viele Bereiche interessant. Bei kamerabasierten Systemen, in denen viele Daten parallel verarbeitet werden müssen, sind Lösungen mit Field-Programmable Gate Arrays (FPGAs) beliebt, da diese bei geringen Kosten hocheffizient sind. Neue Methoden der High-Level Synthese (HLS) versprechen eine noch kostengünstigere Entwicklung mit FPGAs und erhöhen somit zusätzlich die Attraktivität dieser Systeme.

In der Ausgabe 1/2017 der inspect wurde beschrieben, wie eine Integration eines Basler Dart Kameramoduls mit BCON for LVDS-Schnittstelle in ein Embedded-System vorgenommen werden kann und welche Vorteile sich hierdurch ergeben. Davon ausgehend stellt sich die Frage, welche weiteren Aspekte zu betrachten sind, um eine Applikation für ein kamerabasiertes Embedded-System zu erstellen. Am Beispiel einer exemplarischen Fußgängererkennung mittels HLS auf einem FPGA lässt sich dies aufzeigen.

Für bildverarbeitende Systeme, sind meist strenge Echtzeitanforderungen zu erfüllen, um einen flüssigen Video-Stream zu erzeugen oder sofortige Reaktionen einleiten zu können. Um solchen Bedingungen gerecht zu werden und nicht die hohen Kosten von dedizierter Hardware aufbringen zu müssen, sind FPGAs eine effiziente und günstige Lösung.

Field-Programmable Gate Arrays (FPGA)

FPGAs sind frei konfigurierbare Integrierte Schaltungen (IC). Für eine Konfiguration eines FPGAs werden nicht die zeitlichen Abläufe wie bei der Programmierung von Mikrocontrollern oder CPUs beschrieben, sondern die interne Verdrahtung des FPGAs und der Zusammenschluss der internen Logikelemente zueinander. Durch die Bauweise können mit FPGAs stark parallele Strukturen erzeugt werden, welche in der Bildverarbeitung optimal genutzt werden können.

Zur Konfiguration eines FPGAs wird heute üblicherweise eine Hardware Description Language (HDL) verwendet, welche auf einem niedrigen Abstraktionsniveau die Eigenschaft der Hardware beschreibt. In einem direkten Vergleich zu Hochsprachen wie C oder C++ ist jedoch durch die hardwarenahe Beschreibung ein erhöhter Entwicklungsaufwand für die gleiche Applikation notwendig. Um diese Entwicklungszeit zu verkürzen, bieten einige FPGA-Hersteller wie Intel und Xilinx Möglichkeiten zur High-Level Synthese an. Durch diese Methode versprechen die FPGA-Hersteller eine deutlich kürzere Zeit bis zur Markteinführung („time-to-market“), bei leicht erhöhten Ressourcenbedarf und gleichbleibender Rechenleistung. Die HLS-Tools sowohl von Intel als auch von Xilinx unterstützen den OpenCL-Standard.

Open Computing Language (OpenCL)

OpenCL ist ein offener Standard für plattformübergreifende, parallele Applikationen auf heterogenen Systemen. Mittlerweile unterstützen viele Hersteller verschiedenster Hardware den Standard, und somit kann der gleiche Code auf GPUs, CPUs, DSPs, FPGAs, etc. ausgeführt werden. Eine OpenCL-Applikation besteht immer aus zwei Teilen, dem Host-Teil und dem oder den Teilen, die auf den Geräten („devices“) laufen. Der Host ist in der Regel eine CPU, auf der eine gängige C- oder C++-Applikation ausgeführt wird.

In dieser Applikation werden die OpenCL-spezifischen Schnittstellen konfiguriert und die Parameter der späteren Berechnungen gesetzt. Der Host ermittelt zuerst die Anzahl an verfügbaren Devices - der Host kann mehrere verwalten und auch sein eigenes Device sein - bevor er den Devices die jeweiligen Kernel zuweist. Ein Kernel beinhaltet die Logik der Applikation und wird mit OpenCL C beschrieben, einer Programmiersprache, die auf dem C99-Standard basiert. Wurde ein Device konfiguriert bzw. programmiert, kann der Host den Kernel auf dem Device starten, und somit wird die Logik der Applikation auf dem Device ausgeführt.

Soll ein OpenCL-Kernel für ein FPGA synthetisiert werden, ist zusätzlich zu dem Kernel-Code noch ein Board Support Package (BSP) notwendig. Das BSP enthält Board-spezifische Informationen wie die Ein- und Ausgänge eines Systems oder die vorhandenen Ressourcen. Viele BSPs werden von Distributoren oder FPGA-Herstellern bereitgestellt. Ein BSP muss aber ggf. weiter angepasst werden, wenn anwendungsspezifische Schnittstellen hinzukommen. Mittels eines Offline-Compilers kann aus dem BSP und dem OpenCL-Kernel ein Bitstream generiert werden, der direkt auf das Board gespielt werden kann und das FPGA konfiguriert.

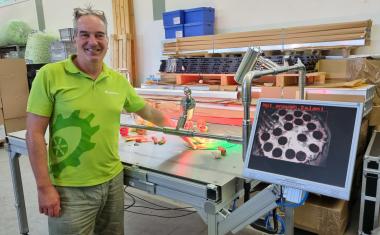

Wurde erfolgreich ein Kamera-Stream in dem BSP erzeugt und eine erste Datenübertragung mittels OpenCL hergestellt, kann anschließend auf den Bilddaten die gewünschte Verarbeitung stattfinden, beispielsweise eine Fußgängererkennung.

Histogram of Oriented Gradients (HOG)

Ein weit verbreiteter Algorithmus zur Personenerkennung ist der Histogram of Oriented Gradients, erstmals veröffentlicht von N. Dalals und B. Triggs. Der Algorithmus basiert darauf, Merkmale (Features) aus dem Bild zu extrahieren und diese anschließend zu klassifizieren. In unserem Anwendungsfall wird der HOG für eine Personendetektion benutzt, kann jedoch durch Anpassung der Klassifizierung für beliebige Objekte eingesetzt werden.

Der Algorithmus arbeitet mit einem gleitenden Detection Window (DW), welches an jeder Stelle des Bildes überprüft, ob sich dort das gesuchte Objekt befindet. Wurde ein Bildbereich klassifiziert, wird das DW pixelweise über das Bild geschoben und somit iterativ das gesamte Bild klassifiziert. Sieht man von der Klassifikation ab, werden vier Schritte in der Applikation durchlaufen.

In einem ersten Schritt wird das Detektionsfenster skaliert, um eine Skalierungsinvarianz zu erzeugen. Hierüber kann zudem die gesuchte Objektgröße eingeschränkt bzw. eingestellt werden. In dem nächsten Schritt werden die Gradienten durch eine einfache [-1 ; 0 ; 1](T)-Maske in x- und y-Richtung des DWs bestimmt.

Für die anschließende Histogrammbildung werden die Länge und die quantisierte Orientierung der Gradienten ermittelt. Zur Bestimmung der quantisierten Orientierung wird der vorzeichenlose Winkel eines Gradienten in eine von acht Klassen (Binnings) eingeteilt. Anschließend werden sogenannte „Zellen“ gebildet. Eine Zelle stellt ein Histogramm dar und besteht aus 8x8 Pixeln bzw. Gradienten.

Innerhalb einer Zelle werden die Längen der Gradienten in ihrem zugehörigen Binning akkumuliert. Ein Binning entspricht in einem Histogramm einer Spalte auf der y-Achse, der Betrag eines Binnings ist über die Länge der zugehörigen Gradienten gegeben.

In dem letzten Schritt vor der Klassifizierung werden 2x2 Zellen zu räumlich überlappenden „Blöcken“ normiert. Die Normierung wird durchgeführt, um Helligkeitsunterschiede innerhalb eines DWs auszugleichen. Die entstandenen Blöcke ergeben das endgültige Bildmerkmal, aus welchen ein Klassifikator (z.B. eine Support Vector Machine (SVM)) ermitteln kann, ob sich in dem DW eine Person befindet.

Fazit

Für Neulinge in dem Bereich der FPGAs ist HLS ein guter Einstieg, da aufgrund der höheren Abstraktion weniger Fehler gemacht werden können. Auch wenn der Ressourcenbedarf noch in den meisten Fällen deutlich höher liegt als bei einem vergleichbaren HDL-Model, so wird an den HLS-Tools kontinuierlich weitergearbeitet, und daher ist die Entwicklung der HLS-Tools mit Sicherheit spannend zu verfolgen. Schon jetzt können HLS-Tools bei einfachen Funktionen mit HDL-Designs mithalten und sind auch für Rapid Prototyping sicherlich zu empfehlen. In detailreichen Anwendungen, in denen möglichst wenige Ressourcen die maximale Rechenleistung erzielen sollen, ist jedoch eine HDL-Implementierung noch zu bevorzugen.