Fraunhofer erweitert Möglichkeiten der Apecs Pilotlinie

09.01.2025 - Mit Förderung des Landes baut das Fraunhofer-Institut für Angewandte Festkörperphysik seine Halbleiter-Forschungsinfrastruktur weiter aus.

Das Fraunhofer IAF erweitert seine technologischen Fähigkeiten im Bereich der III-V-Verbindungshalbleiter und leistet damit einen wertvollen Beitrag zum Aufbau der Pilotlinie Advanced Packaging and Heterogeneous Integration for Electronic Components and Systems „Apecs” im Rahmen des EU Chips Acts. Das Ministerium für Wirtschaft, Arbeit und Tourismus Baden-Württemberg beteiligt sich an der Förderung mit 4,35 Millionen Euro. Am 16. Dezember 2024 übergab Wirtschaftsstaatssekretär Dr. Patrick Rapp der Institutsleitung symbolisch einen Scheck über die Fördersumme. Apecs ermöglicht es, in den kommenden viereinhalb Jahren europaweit die Forschungs- und Entwicklungsinfrastruktur weiter auszubauen und integriert vielversprechende Kerntechnologien, darunter CMOS und III-V für RF, Photonik und Sensoren.

Die Pilotlinie ist ein wichtiger Baustein des EU Chips Acts, um Chiplet-Innovationen voranzutreiben und die Forschungs- und Fertigungskapazitäten für Halbleiter in Europa zu erhöhen. Die in der FMD kooperierenden Institute arbeiten eng mit weiteren europäischen Partnern am Aufbau der Pilotlinie und leisten damit maßgeblich einen Beitrag, Europas technologische Resilienz zu stärken und somit auch die globale Wettbewerbsfähigkeit in der Halbleiterindustrie zu steigern.

Sowohl großen Industrieunternehmen als auch kleinen und mittelständischen Unternehmen (KMU) und Start-ups wird die Pilotlinie einen niederschwelligen Zugang zu Cutting-Edge-Technologien ermöglichen und für sichere, resiliente Halbleiterwertschöpfungsketten sorgen. Apecs wird durch Chips Joint Undertaking und durch nationale Förderungen von Belgien, Deutschland, Finnland, Frankreich, Griechenland, Österreich, Portugal und Spanien im Rahmen der Chips-for-Europe-Initiative kofinanziert. Die Gesamtfinanzierung beläuft sich auf 730 Miollionen Euro über viereinhalb Jahre.

Apecs setzt beim skalierbaren Industrietransfer neu entwickelter Innovationen im Bereich Heterointegration, insbesondere beim Einsatz neuer Chiplet-Technologien an und schlägt so die Brücke zur anwendungsorientierten Forschung. Apecs geht über herkömmliche System-in-Package-Methoden (SiP) hinaus und zielt darauf ab, robuste und vertrauenswürdige heterogene Systeme zu liefern, die die Innovationsfähigkeit der europäischen Halbleiterindustrie erheblich steigern.

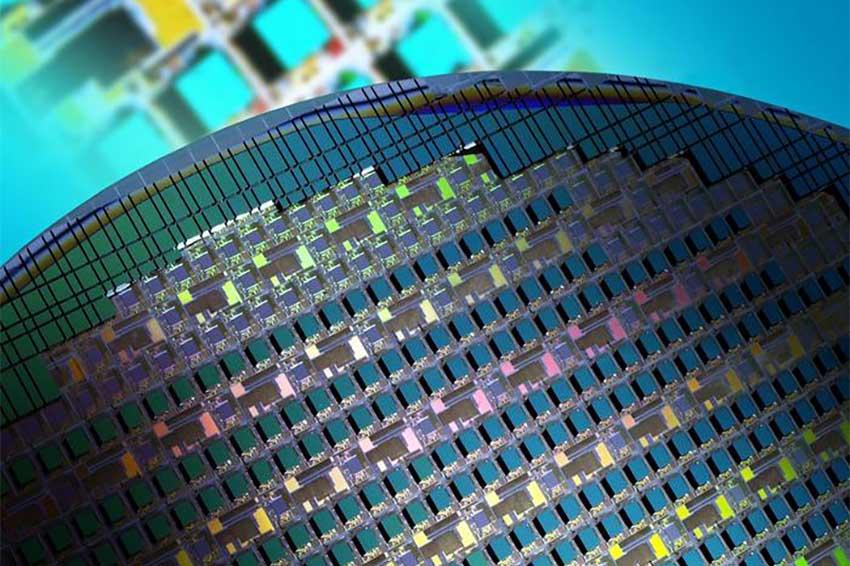

Die steigenden Performance- und Kosten-Anforderungen an elektronische Komponenten führen dazu, dass konventionelle Halbleiter-Chips zunehmend an ihre technologischen Grenzen stoßen. Die Prozessierung großer integrierter Schaltungen, wie sie für umfassende Funktionalitäten erforderlich sind, verursacht hohe Kosten, da einzelne Defekte sich extrem stark auf die Ausbeute eines einzelnen Wafers auswirken. Zudem sorgen chemische und mechanische Unverträglichkeiten verschiedener Materialien und Schichtstrukturen dafür, dass sich nur in begrenztem Umfang unterschiedliche Technologien auf einem Wafer realisieren lassen.

Eine neuartige Lösung, um die Systemfunktionalität effizient zu steigern, besteht in der elektrischen oder optischen Verbindung einzelner kleiner Komponenten (sogenannter Chiplets) auf einem gemeinsamen Substrat (Interposer). Durch den Chiplet-Ansatz können die einzelnen Technologien jeweils die für sie optimale Epitaxie und Prozessierung durchlaufen und bilden im Anschluss durch verlustarme Integration ein hochfunktionales, flexibles und effizientes System auf Chipgröße. Diese Modularisierung erhöht außerdem die Skalierbarkeit, vereinfacht das Chipdesign und verkürzt die Zeit bis zur Markteinführung von Innovationen.

Link: APECS Pilot Line, Fraunhofer-Institut für Photonische Mikrosysteme IPMS, Dresden, Germany

Kontakt

Fraunhofer-Institut für Angewandte Festkörperphysik IAF

Tullastraße 72

79108 Freiburg

Deutschland

+49 761 5159-0

+49 761 5159-400